PCIe从入门到精通之三:PCIe设备的内部组件

0. 引言

PCIe 是硬件工程师跨不过去的坎。我刚开始工作就接触 PCIe,工作中遇到的所有产品都有 PCIe 总线。在此想把自己学习 PCIe 的一些经历和感悟,以及踩过的坑分享在这里,与大家一起进步。

所有 PCIe 主题的文章都会收录在《深入浅出聊 PCIe》合集里,每篇文章涵盖一个 PCIe 的主题,预计会有几十篇文章。

在上一篇文章《PCIe 从入门到精通之二:计算机王国中的 PCIe 设备》中,我们介绍了三类 PCIe device:PCIe Root Complex、PCIe Endpoint 和 PCIe Switch,并着重详细介绍了 Root Complex 内的三个组件:Host Bridge、RCiEP 和 Root Port 的基本功能。在这一篇文章中我们继续介绍 PCIe device 的更多内部组件。

需要下载 PCIe 学习资料的朋友(pdf 格式),请关注本微信公众号“硬件工程师宝典”,在对话框内回复“PCIe”,将获取标准下载链接。

1. PCIe 设备内的组件:Upstream Port、Downstream Port 和 Virtual PCI-PCI Bridge

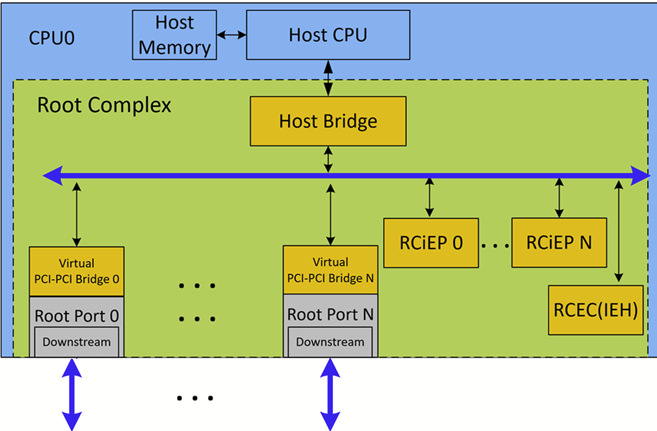

在 PCIe 设备中,“上游端口”(Upstream Port)和“下游端口”(Downstream Port)是根据它们相对于“根联合体”(Root Complex, RC)的方向来定义的,就像总公司向子公司传达命令的方向。如下图所示。

上图是一个 Root Complex 和 PCIe device 直接互联图:

- Root Complex:包含 Virtual PCI-PCI Bridge 和 Downstream Root Port(因为总公司总是向下传达命令的)。

- PCIe device:包含一个 Upstream Port(因为子公司总是向上递交报告的)。

图中蓝色的箭头代表一个 PCIe Bus。Root Complex 通过自身的 Virtual PCI-PCI Bridge 连到自己的 Root Port 上,Root Port 具有向下的 Downstream Port,Endpoint device 上的 Upstream Port 与 Root Complex 的 Downstream Port 相连接。

1.1 上游端口(Upstream Port)

- 定义:指向根联合体(Root Complex)方向的端口。

- 作用:负责将数据和控制信号从设备或 PCIe 交换机发送到更靠近根联合体的方向。

Upstream Port 示例:

- 对于终端设备(Endpoint Device),例如显卡或 SSD,它连接到 CPU(即根联合体)的端口就是上游端口。

- 对于 PCIe 交换机,连接到根联合体或另一个更靠近根联合体的交换机的端口,是该交换机的上游端口。

1.2 下游端口(Downstream Port)

- 定义:远离根联合体(Root Complex)方向的端口。

- 作用:负责将数据和控制信号从根联合体或 PCIe 交换机发送到更远离根联合体的设备。

Downstream Port 示例:

- 对于根联合体本身,其根端口(Root Port)就是下游端口,因为它连接着拓扑结构中更下层的设备。

- 对于 PCIe 交换机,连接到终端设备或另一个更远离根联合体的交换机的端口,是该交换机的下游端口。

1.3 Virtual PCI-PCI Bridge

“虚拟 PCI-PCI 桥”并不是一个像传统 PCI 架构中那样独立的物理桥接芯片,而是一个逻辑概念或软件抽象。它的存在是为了让操作系统(OS)能够沿用 PCI 时代已有的设备枚举和配置机制来管理 PCIe 设备。

可以将“虚拟 PCI-PCI 桥”比拟成一个公司内的项目小组,每个“项目小组”有一个项目名字,我们用 PCIe Bus Number 来命名它。因此每个“虚拟 PCI-PCI 桥”下面有一个独立的 PCIe Bus Number。

- Host Bridge 的 PCIe Bus Number 从 0 开始

- 其他的 PCIe Bus Number 根据系统开机时枚举来确定(关于 PCIe Bus 枚举,后面在专门章节讲解)

每个根端口在软件角度来看都像一个 PCI-PCI 桥,这意味着它拥有一个配置空间,操作系统可以通过这个配置空间进行管理。

简而言之:理解上游和下游的关键在于方向性——数据流向根联合体为“上游”,数据流离根联合体为“下游”。

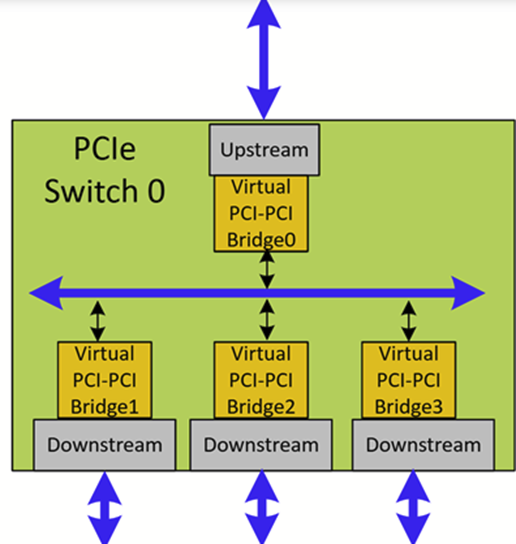

2. PCIe Switch 的内部组件

PCIe 交换机(PCIe Switch)是扩展 PCIe 总线拓扑的关键组件。它通过上游端口和下游端口来管理和路由数据流量:

- 与 Root Complex 联系时:它俯耳倾听,拥有 Upstream Port(可以向上递交报告的权利)

- 与 Endpoint 联系时:它趾高气扬,拥有 Downstream Port(可以向下传达命令的权利)

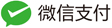

PCIe Switch 角色转换非常丝滑。如下图所示,这个 PCIe Switch 拥有一个 Upstream Port 和三个 Downstream Port,每个 PCIe Port 都和一个 Virtual PCI-PCI Bridge 相连。

PCIe Switch 是唯一一个既有 Upstream Port 又有 Downstream Port 的 PCI device。

- 和 Root Complex 一样,每个“虚拟 PCI-PCI 桥”下面有一个独立的 PCIe Bus

- 图中每一个蓝色的箭头代表一个 PCIe Bus,拥有唯一的 PCIe Bus Number

端口说明:

- 上游端口:连接到 PCIe 层次结构中更高级别(即更靠近根联合体)的端口。一个 PCIe 交换机通常只有一个上游端口(Multi-Host mode 可以有两个 Upstream Port)。

- 下游端口:连接到 PCIe 层次结构中更低级别(即更远离根联合体)的端口。一个 PCIe 交换机通常有多个下游端口,这使得它能够连接多个设备或进一步扩展 PCIe 总线数量。

3. CPU Root Complex 的内部组件

我们再回过头来看看 CPU Root Complex 的内部组件。它作为总公司 CEO 的秘书办,是最复杂的,通常包含:

- Host Bridge

- 若干个 Virtual PCI-PCI Bridge

- 若干个 RCiEP

- 至少一个 Root Port

- 若干个 Root Complex Integrated Endpoint

- 若干个 Root Complex Event Collector(RCEC)

Host Bridge、Virtual PCI-PCI Bridge、RCiEP 和 Root Port 在上一篇文章中介绍过,下面补充介绍 Root Complex Event Collector 和非透明桥(Non-Transparent Bridge)。

上图中 Host CPU 直接与 Host Bridge 相连,Host Bridge 向下分别连接:

- 两个 Root Complex Integrated Endpoint(RCiEP)

- 一个 Root Complex Event Collector(RCEC)

- N 个 Virtual PCI-PCI Bridge

每个“虚拟 PCI-PCI 桥”下面有一个独立的 PCIe Bus,图中每一个蓝色的箭头代表一个 PCIe Bus,拥有唯一的 PCIe Bus Number。

3.1 Root Complex Event Collector(RCEC)

RCEC 相当于 Root Complex 的情报机构,也是一个 Root Complex 的内部 PCIe device。它的主要作用是:

收集和处理来自 PCIe 层次结构中特定设备(特别是根联合体集成终端设备 RCiEP)的各种事件消息,并将其报告给系统软件(如操作系统或固件)。

- RCEC 是专门为支持 RCiEP 而设计的

- RCiEP 是直接集成在根联合体内部的 PCIe 终端设备(例如某些 CPU 内部的集成显卡或存储控制器)

注意:RCEC 在 PCIe 规范中是一个可选组件。在某些平台中,可能存在硬件执行类似功能但对操作系统不可见的情况,或者通过 ACPI 平台错误接口(APEI)等其他机制来报告错误。但在支持 RCEC 的系统中,它提供了一个标准化的接口来处理这些重要的系统事件。Intel 将 RCEC 集成在 IEH(Integrated Error Handler)里。

4. 透明桥与非透明桥

4.1 透明桥(Transparent Bridge)

在一个集团公司内部(一个 PCIe 体系 Hierarchy 内),总公司(Root Complex)、区域总公司(Switch)和子公司(Endpoint)大家都在一个局域网内,内部的信息和资源是完全公开共享的。

因此 Root Complex、Switch 和 Endpoint 之间的 Memory Space 和 Configuration Space 等信息都相互可以访问——就像“Endpoint 今天穿的内裤的颜色,Root Complex 一清二楚”,大家都是透明的。

处于同一个 PCIe 体系 Hierarchy 内,前面提到的 Root Complex 和 PCIe Switch 内部的 Virtual PCI-PCI Bridge 都是工作在透明模式(白盒模式),其工作方式和所有信息对系统是可见的,我们称之为透明桥(Transparent Bridge, TB)。

透明桥将两个连接的总线域合并到一个统一的地址空间中,并将它们视为一个统一的地址域。

4.2 非透明桥(Non-Transparent Bridge)

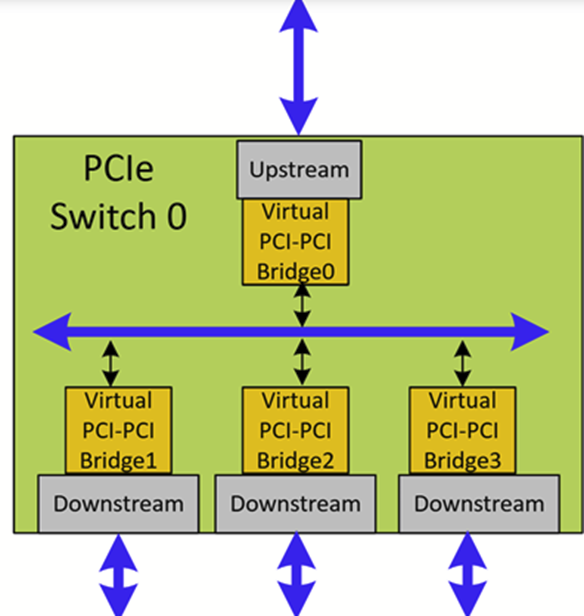

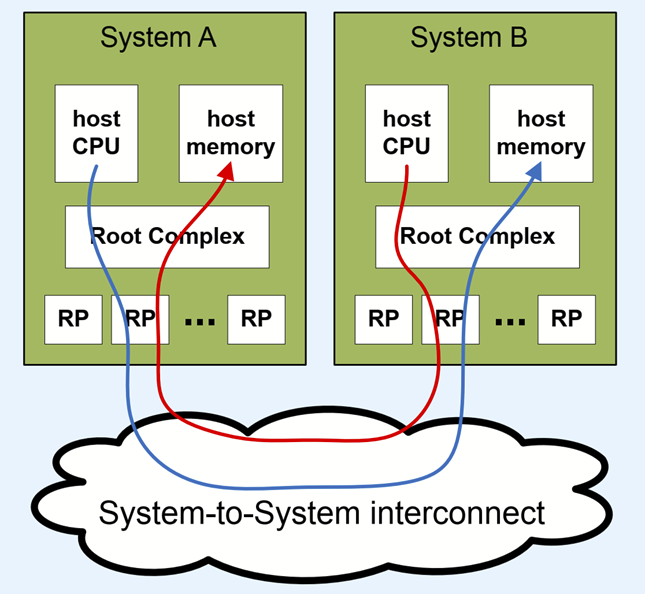

两个集团公司(两个不同的 PCIe 体系 Hierarchy)之间有可能建立长期的战略合作伙伴关系,它们之间需要经常的大规模的业务往来(数据交换)。两个集团公司可以各自指派一个代表(Contact Window,即 PCIe Bridge)直接联系处理。

例如:

- 一个 CPU 系统和另一个 CPU 系统通过 Root Port 的 PCIe Bridge 互联

- 一个 CPU 系统和另一个 CPU 系统通过 PCIe Switch 的 Non-Transparent Bridge 互联

这两名 Contact Window(PCIe Bridge)只负责交换信息,关于公司内部的运营情况和数据是机密,大家相互之间都守口如瓶。两个 PCIe 体系的 Memory Space 和 Configuration Space 等信息都相互屏蔽,它们都工作在非透明模式(黑盒模式),我们称之为非透明桥(Non-Transparent Bridge, NTB)。

非透明桥是一种特殊的 PCIe 桥接器,它不将两个连接的总线域合并到一个统一的地址空间中,而是将它们视为两个独立的地址域。

PCI Express 非透明桥接器(NTB)起到了桥梁的作用,能够实现两个 PCI Express 体系(例如本地系统和远程系统)之间的高性能、低延迟通信。NTB 允许本地处理器独立配置和控制本地系统,并将本地主机内存域与远程主机内存域隔离开来,同时实现两个域之间的状态和数据交换。本地处理器会将 NTB 视为根复杂集成端点(RCiEP)来进行识别。

4.3 透明桥和非透明桥区别总结

| 特征 | 透明桥(Transparent Bridge) | 非透明桥(Non-Transparent Bridge, NTB) |

|---|---|---|

| 地址空间 | 合并为一个统一的地址空间,主机“看到”所有下游设备 | 隔离的独立地址空间,每个主机只“看到”NTB 本身作为终端设备 |

| 主机可见性 | 对主机透明,主机直接枚举和访问下游设备 | 对主机不透明,主机将 NTB 视为一个终端设备 |

| 主要功能 | 扩展 PCIe 总线,连接更多设备 | 连接独立的 PCIe 域/处理器,实现域间隔离和通信 |

| 通信方式 | 直接路由事务 | 通过地址转换、共享内存窗口、Scratchpad 和 Doorbell 寄存器进行 |

| 应用场景 | 标准 PCIe 拓扑扩展,如 PCIe 交换机、根端口 | 多主机系统、高可用性/冗余系统、智能 I/O、专用数据传输 |

简而言之:透明桥是用于构建和扩展单一 PCIe 树的标准方式,而 NTB 则是一种高级功能,用于在需要隔离和独立管理多个 PCIe 域(通常是多个处理器或子系统)时实现它们之间的通信。

5. 非透明桥(Non-Transparent Bridge)在哪里?

5.1 透明桥模式和非透明模式

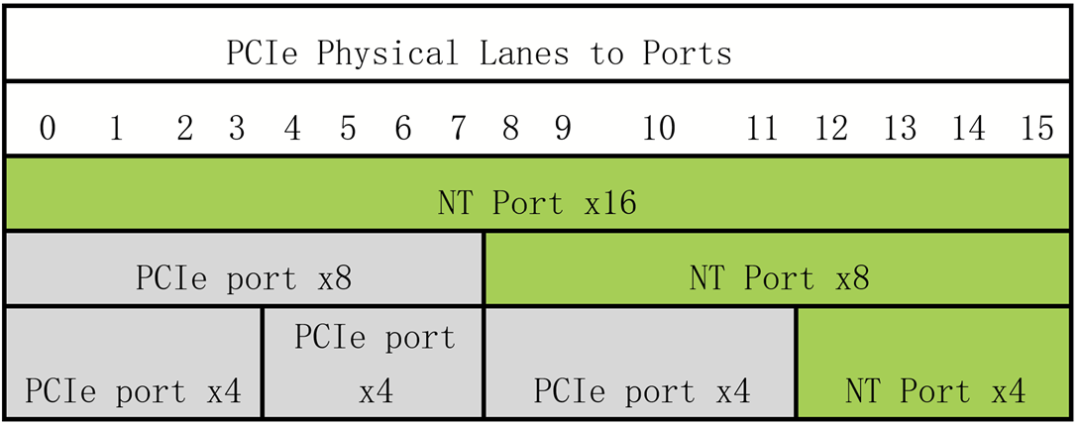

下面两幅图分别是 CPU 和 Switch 的内部组件图,从图中我们根本找不到非透明桥(Non-Transparent Bridge)在哪里。

其实图中的 Virtual PCI-PCI Bridge 既可以工作在透明桥模式,又可以工作在非透明桥模式。因此合二为一在一个 Root Port 实体上,而且一个 Root Port 只需要一个 device 充当非透明桥——毕竟两个公司之间的 contact window 只要一对就可以了。

5.2 嫡长子袭爵

一个 Root Port 一般有 16 个 Lane,可以通过 bifurcation 被均分为两个或四个 devices(Intel 给这个功能起了个时尚的新名字叫 subdivision)。不管是 bifurcation 还是 subdivision,其实就是“分家”。

“分家”时,“财富”(Lanes)可以在儿子之间均等分配,一碗水端平。但是只有一个非透明桥的角色,分配给哪个儿子?其实老祖宗早就给出了答案:世袭罔替的爵位不都是由嫡长子承袭吗?

那么问题又来了,谁是嫡长子?

下图是一个 x16 Lane 的 PCIe IO 在不同的 bifurcation 情况,这个 PCIe IO 可以工作在 x16 模式、x8 模式或 x4 模式。在 PCI Express x16 IIO 模块中,只能将一个 Root Port 配置为非透明桥端口。

- 灰色的 Lane:表示充当一般的 PCIe 角色

- 绿色的 Lane:表示充当非透明桥的角色(嫡长子就是从物理 Lane 的编号最大者开始向编号小的选择)

这里可千万不要连错了,否则只能 respin 我们的 layout 了,血淋淋的教训啊!

PCIe Physical Lanes to Ports 映射表:

| 配置 | Lane 0-15 映射情况 |

|---|---|

| NT Port x16 | Lane 0-15 全部为 NT Port |

| PCIe Port x8 | Lane 0-7 为 PCIe Port |

| NT Port x8 | Lane 8-15 为 NT Port |

| PCIe Port x4 | Lane 0-3 为 PCIe Port |

| NT Port x4 | Lane 12-15 为 NT Port |

在非透明桥端口为 x16 的情况下,NT 端口总是映射到从第 15 到第 0 的最高位物理通道。对于非透明桥端口为 x8 的情况,它从物理通道 15 到 8 映射;而对于非透明桥端口为 x4 的情况,则从物理通道 15 到 12 映射。

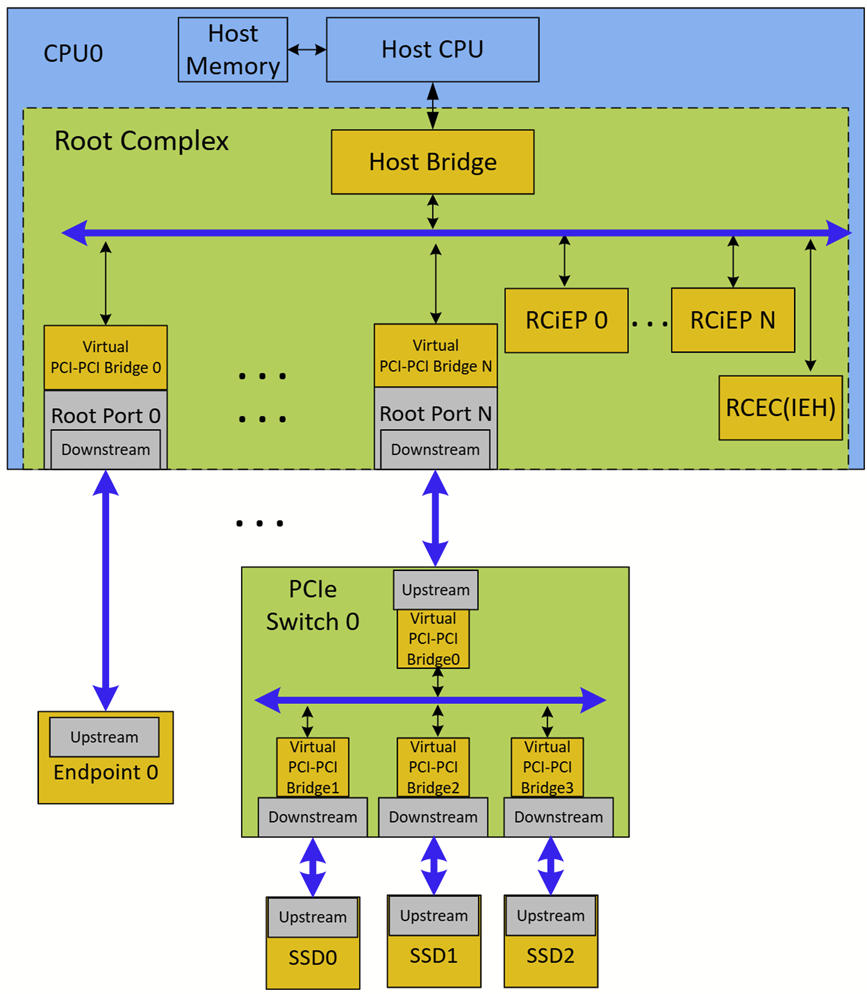

6. 大团圆

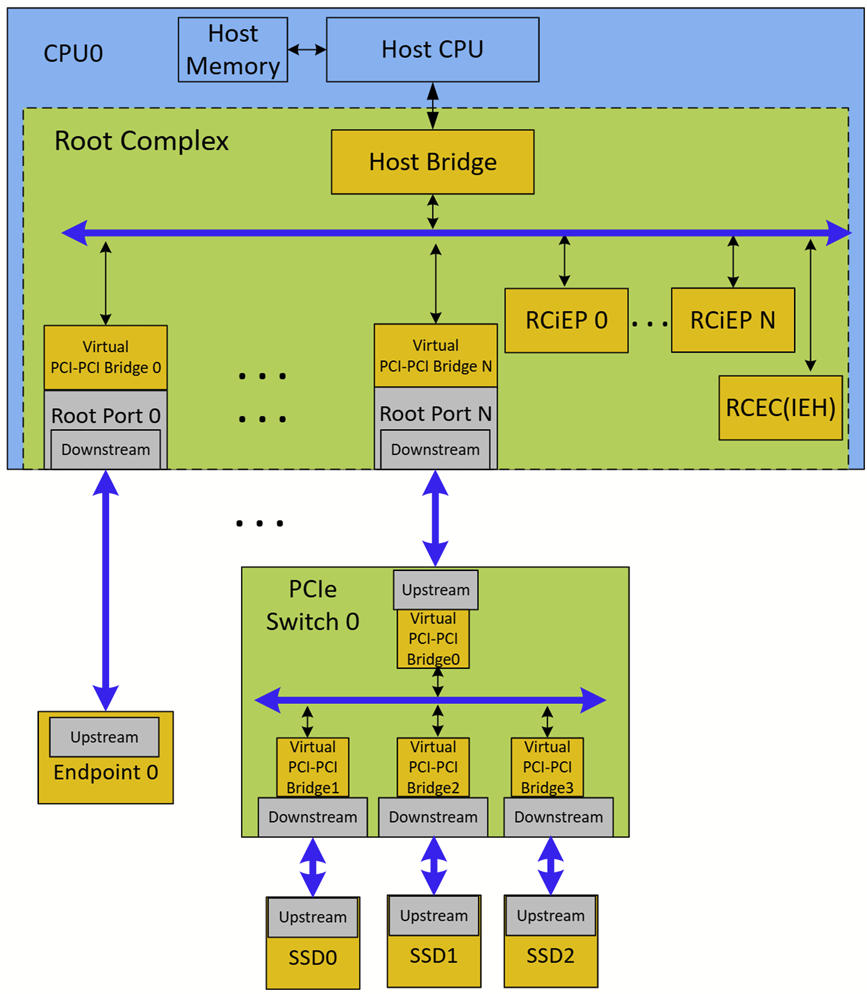

前面我们分别将 Root Complex、Switch 和 Endpoint 掰开了、揉碎了讲解了一遍。是时候让它们团聚了!

上图是将它们合并到一起的样子(敲黑板:这张图在以后的很多章节中都会用到)。

- 黄色的组件:是拥有 PCIe 配置空间的 device

- PCIe Switch 下面挂载着三个 NVMe SSD

下一章我们将以这张图为中心,介绍 PCIe 总线的拓扑结构(Topology)。

这篇文章就聊到这里,敬请关注下一篇:

《PCIe 从入门到精通之四:PCIe 总线的拓扑结构》

参考文献

- PCI Express® Base Specification Revision 5.0 Version 1.0

- PCI Express® Base Specification Revision 6.4

- PCI Express® Base Specification Revision 7.0

PCIe从入门到精通

PCIe从入门到精通